大阪大学 量子情報・量子生命研究センターと富士通は2023年3月23日、現行コンピュータの計算性能を超える量子コンピュータの実用化を早める技術として「高効率位相回転ゲート式量子計算アーキテクチャ」を確立したと発表した。量子エラー訂正に必要な物理量子ビット数を大幅に低減する。現行の性能を超える64論理量子ビットの量子コンピュータを1万物理量子ビットで構築可能としている。

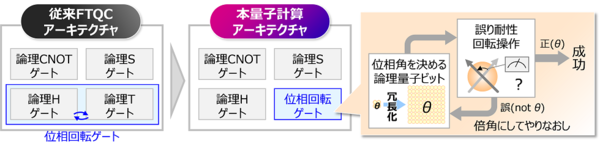

大阪大学 量子情報・量子生命研究センターと富士通は、現行コンピュータの計算性能を超える量子コンピュータの実用化を早める技術として「高効率位相回転ゲート式量子計算アーキテクチャ」を確立したと発表した(図1)。

図1:大阪大学と富士通が確立した「高効率位相回転ゲート式量子計算アーキテクチャ」の概要(出典:大阪大学、富士通)

図1:大阪大学と富士通が確立した「高効率位相回転ゲート式量子計算アーキテクチャ」の概要(出典:大阪大学、富士通)拡大画像表示

富士通は、量子コンピュータが本来の性能を発揮するには、複数の物理量子ビットから1つの論理量子ビットを形成し、量子ビットに冗長性を持たせることで、発生した量子エラーを訂正しながら計算する量子エラー訂正技術がカギとなると説明している。

「従来のFTOC(Fault Tolerant Quantum Computer:誤り耐性量子コンピュータ)アーキテクチャでは、量子エラー訂正に100万以上の物理量子ビットが必要と言われている。物理量子ビット数が今後1万程度に到達した段階で量子エラー訂正を実行しても、計算可能な規模は極めて小さく、現行のコンピュータの処理能力を超えることは不可能と考えられていた」(富士通)

今回確立した量子計算アーキテクチャでは、従来のFTQCアーキテクチャとは異なる基本量子ゲートセットを新たに定義し、特に大量の物理量子ビットと量子ゲート操作が必要だった位相回転操作を高効率で実行する位相回転ゲートを世界で初めて導入する。

位相回転ゲートにより、物理量子ビットを従来の10分の1以下に低減し、任意回転の実行にかかるゲート操作回数を従来の20分の1程度に低減する。また、量子エラー確率は、物理量子ビットでの量子エラー確率の約8分の1まで抑えて高精度な計算を可能にする。 これらにより、現行コンピュータの最高性能の約10万倍に相当する64論理量子ビットの量子コンピュータを、1万物理量子ビットで構築が可能になるという。